# 6818

## DABiC-IV, 32-BIT SERIAL-INPUT, LATCHED SOURCE DRIVER

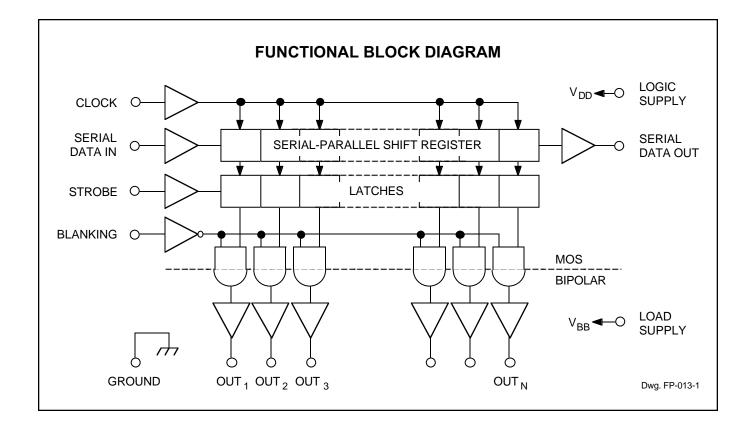

The A6818– devices combine a 32-bit CMOS shift register, accompanying data latches and control circuitry with bipolar sourcing outputs and pnp active pull downs. Designed primarily to drive vacuum-fluorescent displays, the 60 V and - 40 mA output ratings also allow these devices to be used in many other peripheral power driver applications. The A6818– features an increased data input rate (compared with the older UCN/UCQ5818–F) and a controlled output slew rate.

The CMOS shift register and latches allow direct interfacing with microprocessor-based systems. With a 3.3 V or 5 V logic supply, typical serial-data input rates are up to 33 MHz.

A CMOS serial data output permits cascade connections in applications requiring additional drive lines. Similar devices are available as the A6810–(10 bits) and A6812–(20 bits).

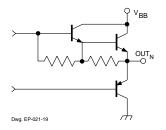

The A6818– output source drivers are npn Darlingtons, capable of sourcing up to 40 mA. The controlled output slew rate reduces electromagnetic noise, which is an important consideration in systems that include telecommunications and/or microprocessors and to meet government emissions regulations. For inter-digit blanking, all output drivers can be disabled and all sink drivers turned on with a BLANKING input high. The pnp active pull-downs will sink at least 2.5 mA.

Three temperature ranges are available for optimum performance in commercial (suffix S-), industrial (E-), and extended industrial (K-) applications. The package style provided is the minimum-area surface-mount PLCC (suffix -EP). Copper lead frames, low logic-power dissipation, and low output-saturation voltages allow these devices to drive most multiplexed vacuum-fluorescent displays over the maximum operating temperature range.

The lead (Pb) free versions have 100% matte tin leadframe plating.

#### FEATURES

- Controlled Output Slew Rate

- 60 V Minimum

- Output Breakdown

- PNP Active Pull-Downs

Low-Power CMOS Logic and Latches

- High-Speed Data Storage

- High Data Input Rate

- Low Output-Saturation VoltagesImproved Replacements

- for SN75518N, SN75518NF, UCN5818–, and UCQ5818–

Always order by complete part number:

| Part Number                | Pb-free  | Packing                | Ambient Temperature, T <sub>A</sub><br>(°C) |

|----------------------------|----------|------------------------|---------------------------------------------|

| A6818EEP<br>A6818EEP-T     | –<br>Yes | 27 pieces/tube         | -40 to 85                                   |

| A6818EEPTR<br>A6818EEPTR-T | –<br>Yes | 450 pieces/13-in. reel | -40 10 85                                   |

| A6818KEP<br>A6818KEP-T     | –<br>Yes | 27 pieces/tube         | -40 to 125                                  |

| A6818KEPTR<br>A6818KEPTR-T | –<br>Yes | 450 pieces/13-in. reel | -40 10 123                                  |

| A6818SEP<br>A6818SEP-T     | –<br>Yes | 27 pieces/tube         |                                             |

| A6818SEPTR<br>A6818SEPTR-T | –<br>Yes | 450 pieces/13-in. reel | –20 to 85                                   |

| A6818xEP                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                              |

| 7  39    8  38    9  37    10  36    11  35    12  34    13  33    14  32    15  31    16  30    17  29                                                                                                                                                                                      |

| ABSOLUTE MAXIMUM RATINGS                                                                                                                                                                                                                                                                     |

| at $T_A = 25^{\circ}C$<br>Logic Supply Voltage, $V_{DD}$ 7.0 V<br>Driver Supply Voltage, $V_{BB}$                                                                                                                                                                                            |

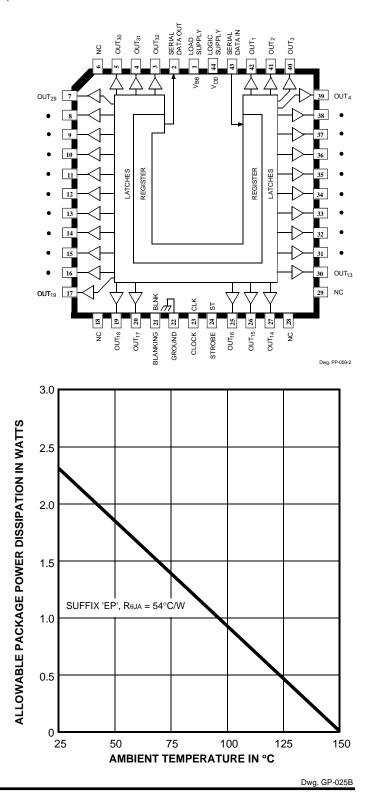

| Package Power Dissipation,      See Graph        Operating Temperature Range, T <sub>A</sub> (Suffix 'E-')        (Suffix 'K-')      -40°C to +85°C        (Suffix 'K-')      -40°C to +125°C        (Suffix 'S-')      -20°C to +85°C        Storage Temperature Range,      T <sub>S</sub> |

| Caution: These CMOS devices have input<br>static protection (Class 2) but are still<br>susceptible to damage if exposed to<br>extremely high static electrical charges.                                                                                                                      |

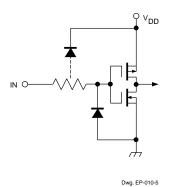

**TYPICAL INPUT CIRCUIT**

A6818xEP

#### TYPICAL OUTPUT DRIVER

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000 Copyright © 1998, 2003 Allegro MicroSystems, Inc.

| Serial |                | Shift Register Contents |                |                | Serial               |                  | Latch Contents   |                 |                |                |                |  | Output Contents  |                |          |                |                |                |  |                  |                |

|--------|----------------|-------------------------|----------------|----------------|----------------------|------------------|------------------|-----------------|----------------|----------------|----------------|--|------------------|----------------|----------|----------------|----------------|----------------|--|------------------|----------------|

|        | Clock<br>Input |                         | I <sub>2</sub> | I <sub>3</sub> | <br>I <sub>N-1</sub> | I <sub>N</sub>   | Data<br>Output   | Strobe<br>Input | I <sub>1</sub> | I <sub>2</sub> | I <sub>3</sub> |  | I <sub>N-1</sub> | I <sub>N</sub> | Blanking | I <sub>1</sub> | l <sub>2</sub> | I <sub>3</sub> |  | I <sub>N-1</sub> | I <sub>N</sub> |

| н      | Ч              | н                       | R <sub>1</sub> | $R_2$          | <br>R <sub>N-2</sub> | R <sub>N-1</sub> | R <sub>N-1</sub> |                 |                |                |                |  |                  |                |          |                |                |                |  |                  |                |

| L      | Ч              | L                       | R <sub>1</sub> | $R_2$          | <br>R <sub>N-2</sub> | R <sub>N-1</sub> | R <sub>N-1</sub> |                 |                |                |                |  |                  |                |          |                |                |                |  |                  |                |

| Х      | l              | R <sub>1</sub>          | $R_2$          | $R_3$          | <br>R <sub>N-1</sub> | R <sub>N</sub>   | R <sub>N</sub>   |                 |                |                |                |  |                  |                |          |                |                |                |  |                  |                |

|        |                | х                       | Х              | Х              | <br>Х                | Х                | х                | L               | R <sub>1</sub> | $R_2$          | $R_3$          |  | R <sub>N-1</sub> | $R_N$          |          |                |                |                |  |                  |                |

|        |                | Р <sub>1</sub>          | $P_2$          | $P_3$          | <br>P <sub>N-1</sub> | P <sub>N</sub>   | P <sub>N</sub>   | Н               | P <sub>1</sub> | P <sub>2</sub> | $P_3$          |  | P <sub>N-1</sub> | $P_N$          | L        | Р <sub>1</sub> | P <sub>2</sub> | $P_3$          |  | P <sub>N-1</sub> | P <sub>N</sub> |

|        |                |                         |                |                |                      |                  |                  |                 | Х              | Х              | Х              |  | Х                | Х              | Н        | L              | L              | L              |  | L                | L              |

#### **TRUTH TABLE**

L = Low Logic Level H = High Logic Level X = Irrelevant P = Present State R = Previous State

## ELECTRICAL CHARACTERISTICS at $T_A = +25^{\circ}C$ (A6818S-) or over operating temperature range (A6818E- and A6818K-), $V_{BB} = 60$ V unless otherwise noted.

|                                |                        |                                                       | Limits | @ V <sub>DD</sub> | = 3.3 V | Limit |        |      |       |

|--------------------------------|------------------------|-------------------------------------------------------|--------|-------------------|---------|-------|--------|------|-------|

| Characteristic                 | Symbol                 | Test Conditions                                       | MIn.   | Тур.              | Max.    | Min.  | Тур.   | Max. | Units |

| Output Leakage Current         | I <sub>CEX</sub>       | V <sub>OUT</sub> = 0 V                                | _      | <-0.1             | -15     | —     | <-0.1  | -15  | μA    |

| Output Voltage                 | V <sub>OUT(1)</sub>    | I <sub>OUT</sub> = -25 mA                             | 57.5   | 58.3              | _       | 57.5  | 58.3   |      | V     |

|                                | V <sub>OUT(0)</sub>    | I <sub>OUT</sub> = 1 mA                               | —      | 1.0               | 1.5     | —     | 1.0    | 1.5  | V     |

| Output Pull-Down Current       | I <sub>OUT(0)</sub>    | $V_{OUT} = 5 V \text{ to } V_{BB}$                    | 2.5    | 5.0               | _       | 2.5   | 5.0    |      | mA    |

| Input Voltage                  | V <sub>IN(1)</sub>     |                                                       | 2.2    | _                 | _       | 3.3   | _      | _    | V     |

|                                | V <sub>IN(0)</sub>     |                                                       | —      | —                 | 1.1     | -     | _      | 1.7  | V     |

| Input Current                  | I <sub>IN(1)</sub>     | $V_{IN} = V_{DD}$                                     | _      | <0.01             | 1.0     | —     | <0.01  | 1.0  | μΑ    |

|                                | I <sub>IN(0)</sub>     | V <sub>IN</sub> = 0.8 V                               | _      | <-0.01            | -1.0    | —     | <-0.01 | -1.0 | μA    |

| Input Clamp Voltage            | V <sub>IK</sub>        | I <sub>IN</sub> = -200 μA                             | —      | -0.8              | -1.5    | —     | -0.8   | -1.5 | V     |

| Serial Data Output Voltage     | V <sub>OUT(1)</sub>    | I <sub>OUT</sub> = -200 μA                            | 2.8    | 3.05              | _       | 4.5   | 4.75   |      | V     |

|                                | V <sub>OUT(0)</sub>    | I <sub>OUT</sub> = 200 μA                             | _      | 0.15              | 0.3     | —     | 0.15   | 0.3  | V     |

| Maximum Clock Frequency        | f <sub>c</sub>         |                                                       | 10     | 33                | _       | 10    | 33     | _    | MHz   |

| Logic Supply Current           | I <sub>DD(1)</sub>     | All Outputs High                                      | —      | 0.25              | 0.75    | —     | 0.3    | 1.0  | mA    |

|                                | I <sub>DD(0)</sub>     | All Outputs Low                                       | —      | 0.25              | 0.75    | -     | 0.3    | 1.0  | mA    |

| Load Supply Current            | I <sub>BB(1)</sub>     | All Outputs High, No Load                             | —      | 4.5               | 9.0     | -     | 4.5    | 9.0  | mA    |

|                                | I <sub>BB(0)</sub>     | All Outputs Low                                       | —      | 0.2               | 20      | -     | 0.2    | 20   | μA    |

| Blanking-to-Output Delay       | t <sub>dis(BQ)</sub>   | C <sub>L</sub> = 30 pF, 50% to 50%                    | —      | 0.7               | 2.0     | —     | 0.7    | 2.0  | μs    |

|                                | t <sub>en(BQ)</sub>    | C <sub>L</sub> = 30 pF, 50% to 50%                    | _      | 1.8               | 3.0     | —     | 1.8    | 3.0  | μs    |

| Strobe-to-Output Delay         | t <sub>p(STH-QL)</sub> | $R_L$ = 2.3 k $\Omega$ , $C_L \le$ 30 pF              | —      | 0.7               | 2.0     | -     | 0.7    | 2.0  | μs    |

|                                | t <sub>p(STH-QH)</sub> | $R_L$ = 2.3 k $\Omega$ , $C_L \le$ 30 pF              | —      | 1.8               | 3.0     | —     | 1.8    | 3.0  | μs    |

| Output Fall Time               | t <sub>f</sub>         | $R_L$ = 2.3 k $\Omega$ , $C_L \le$ 30 pF              | 2.4    | —                 | 12      | 2.4   | —      | 12   | μs    |

| Output Rise Time               | tr                     | $R_L = 2.3 \text{ k}\Omega, \ C_L \leq 30 \text{ pF}$ | 2.4    | _                 | 12      | 2.4   | —      | 12   | μs    |

| Output Slew Rate               | dV/dt                  | $R_L$ = 2.3 k $\Omega$ , $C_L \le 30 \text{ pF}$      | 4.0    | _                 | 20      | 4.0   | _      | 20   | V/µs  |

| Clock-to-Serial Data Out Delay | t <sub>p(CH-SQX)</sub> | I <sub>OUT</sub> = ±200 μA                            | _      | 50                | _       | —     | 50     |      | ns    |

Negative current is defined as coming out of (sourcing) the specified device terminal.

Typical data is is for design information only and is at  $T_A$  = +25°C.

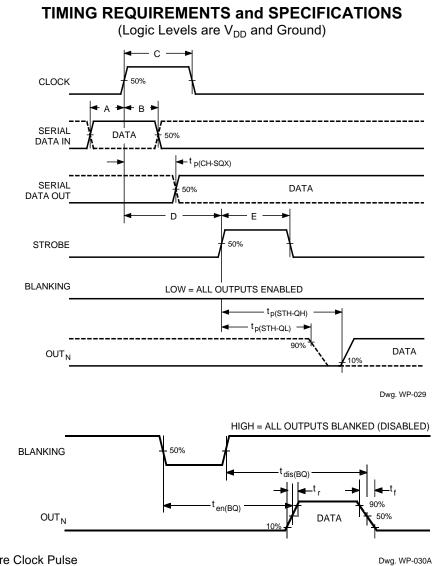

#### A. Data Active Time Before Clock Pulse

| (Data Set-Up Time), t <sub>su(D)</sub> 25                                                      | ns |

|------------------------------------------------------------------------------------------------|----|

| B. Data Active Time After Clock Pulse                                                          |    |

| (Data Hold Time), t <sub>h(D)</sub> 25                                                         | ns |

| $\textbf{C. Clock Pulse Width, } t_{w(CH)} \qquad \qquad \textbf{50}$                          | ns |

| <b>D.</b> Time Between Clock Activation and Strobe, $t_{\text{su}(C)}$ 100                     | ns |

| E. Strobe Pulse Width, $t_{w(STH)}$ 50                                                         | ns |

| NOTE – Timing is representative of a 10 MHz clock. Significantly higher speeds are attainable. |    |

Serial Data present at the input is transferred to the shift register on the logic "0" to logic "1" transition of the CLOCK input pulse. On succeeding CLOCK pulses, the registers shift data information towards the SERIAL DATA OUTPUT. The SERIAL DATA must appear at the input prior to the rising edge of the CLOCK input waveform. Information present at any register is transferred to the respective latch when the STROBE is high (serial-to-parallel conversion). The latches will continue to accept new data as long as the STROBE is held high. Applications where the latches are bypassed (STROBE tied high) will require that the BLANKING input be high during serial data entry.

When the BLANKING input is high, the output source drivers are disabled (OFF); the pnp active pull-down sink drivers are ON. The information stored in the latches is not affected by the BLANKING input. With the BLANKING input low, the outputs are controlled by the state of their respective latches.

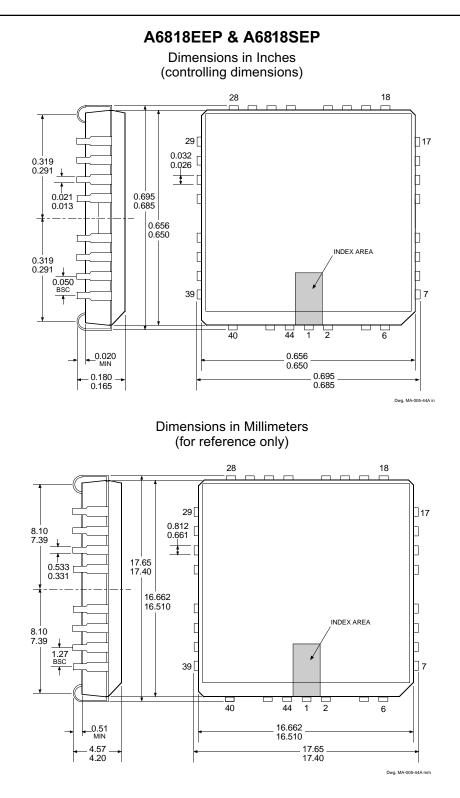

NOTES: 1. Exact body and lead configuration at vendor's option within limits shown.

2. Lead spacing tolerance is non-cumulative.

The products described here are manufactured under one or more U.S. patents or U.S. patents pending.

Allegro MicroSystems, Inc. reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro products are not authorized for use as critical components in life-support devices or systems without express written approval.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, Inc. assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

115 Northeast Cutoff, Box 15036 Worcester, Massachusetts 01615-0036 (508) 853-5000